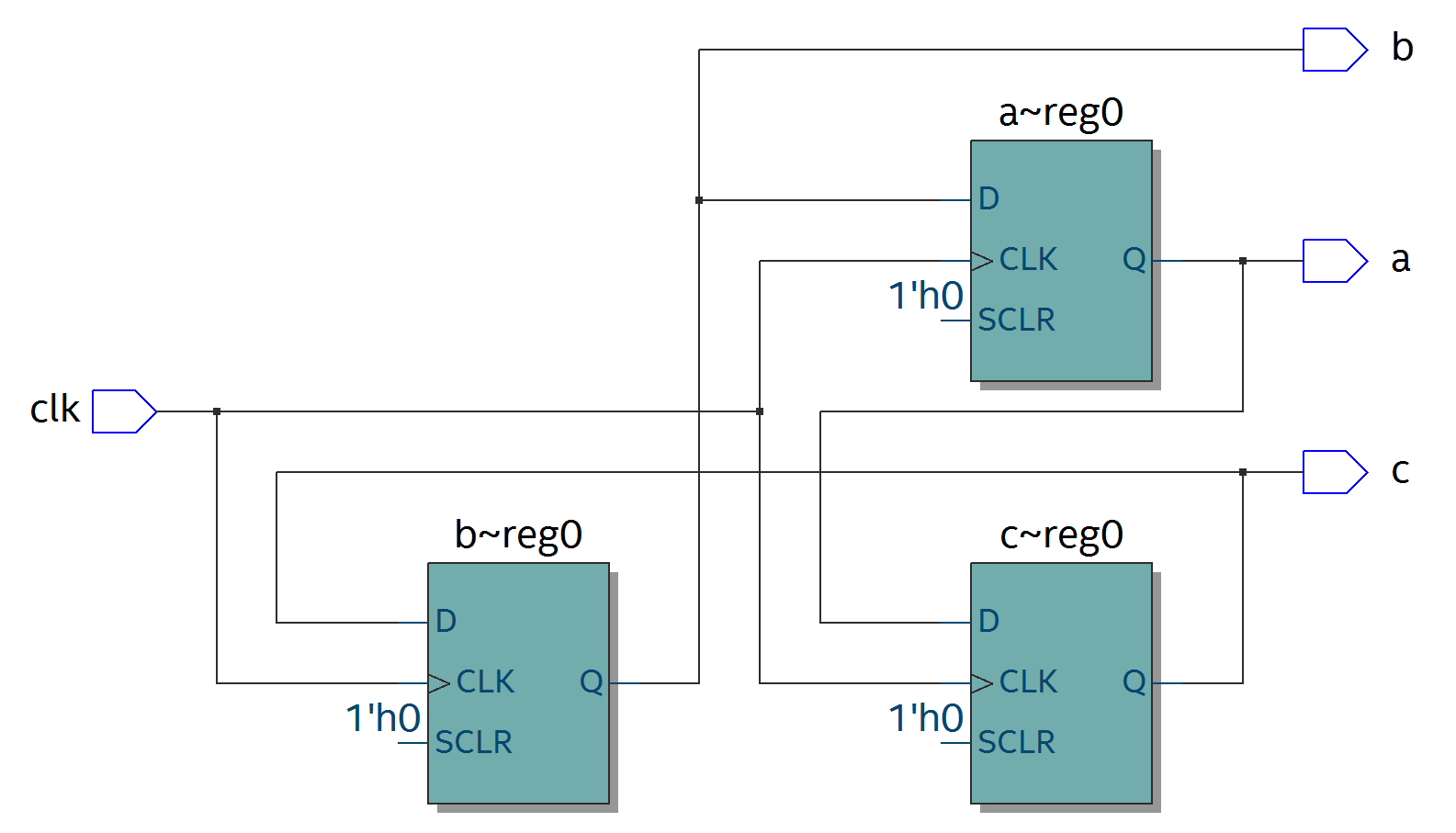

Always@ (posedge CLK) begin Q 0Jul 12, · 遅延サイクルと幅を設定可能なシフトレジスタです。 意外とネットに記述が見当たらないので作成しました。 FF生成は本モジュールをパラメーターを変えて使いまわすと楽そう。 Shift Register Module ModelSimで動作確認し、Quartus131にて実装確認を行いました。シフトレジスタ シフトレジスタは複数のDFFを直列に接続した回路です。 この回路を素直にHDLへ変換すると下の様になります。 reg 30 Q ;

Fpga ジャジャガッチブログ

Verilog hdl シフトレジスタ

Verilog hdl シフトレジスタ-シフトレジスタ 0711 Verilog VHDL 回路設計 シフトレジスタはDFFを連ねた回路ですが、いろいろな回路の基本となる事が多く、必ずマスターしておかなくてはならない回路構成です。 単純なシフトレジスタは入力の信号をクロック分遅延させる。 という回路になります。 この動作を応用して、シリアルデータの生成やその逆、高度な物ですと、ランダマイザや101 Innovation Drive San Jose, CA wwwalteracom UG ユーザーガイド RAMベースのシフト・レジスタ (ALTSHIFT_TAPS)メガファンクション

デジタル回路設計veriloghdl通信講座 技術系通信講座のシーモス

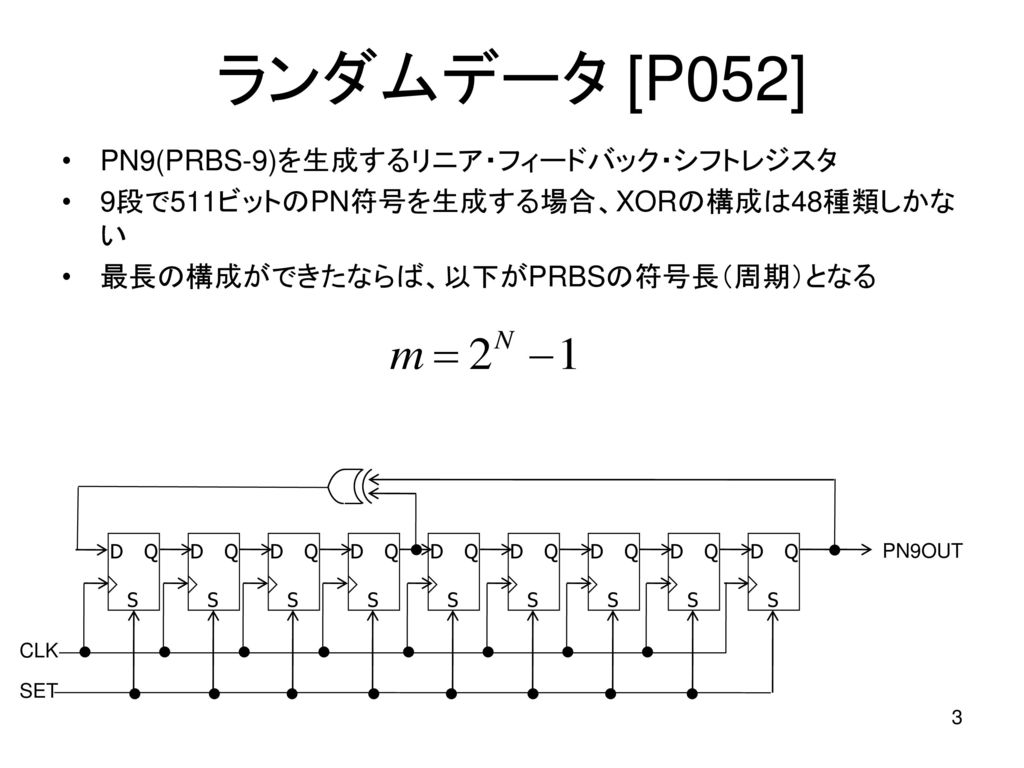

これは、多項式 X^9X^51 の ガロアLFSR (線形帰還シフトレジスタ) で、 2^9=512 通り の内、0 を除いた 511通りの値を周期的に変化する。 512番目の値が最初の値と同じになる。ホワイト ペーパ デザイン パフォーマンス向上のための HDL コーディング法 WP231 (11) 06 年 1 月 6 日 wwwxilinxcojp 3 R け、シフト レジスタのリセットを使用しない。 乗算器と RAM 最新のザイリンクス FPGA アーキテクチャでは、すべてに専用の演算リソースがあ ります。Feb 06, 17 · レジスタの動作は、図2のようにボールが摩擦の無いひとつの山を移動する状態に例えて表すことができます。山の両側は安定した状態(High または Low)を表していて、山の頂上がメタステーブルの状態を表しています。

VerilogHDLファイルの追加 10 "Add items to the Project"ウィンドウ︓Add Existing File またはメインウィンドウからProject→Add to Project→Existing File "Add file to Project"ウィンドウ︓Brows "Select files to add to project"ウィンドウ︓ c/J2/Verilogeqvを選択して開く.HDL/SystemVerilogでは多次元配列を扱えるようになった。 いまさら例を出すまでもないが、8bit長のレジスタを宣言するには、以下のようにしていた。 reg 70 a;Reg レジスタ宣言: 値を保持する変数に対して宣言する。 wire ワイヤ宣言: 配線として使用する変数に対して宣言する。 (assign 文によって常時右辺の結果を出力する) なれないうちは使い分けが難しいので ・always 内で左辺として利用する場合はreg 宣言。

25 Verilog での記述 19 この場合X の1 ビットシフトを計算し、その結果をどこかにとっておく必要があ 定義してやる。ここで、入力には、値を保持するためレジスタ(reg) として宣言し、Dec 05, 16 · クロックなどの信号の変化のタイミングでレジスタに値を代入するような処理を行いたい場合は、alwaysで起動される文において、レジスタ型(reg型)変数へノンブロッキング代入Apr , · 目的 多ビット信号の配列(二次元配列)を使用する。 宣言 レジスタ(メモリ) reg 70 r_data0127 // 8bit幅 128 個のレジスタ宣言 信号(Wire) wire 70 w_data0127 // 8bit幅 128 組の ワイヤ宣言 Verilog では ポートに二次元配列は使用できない。

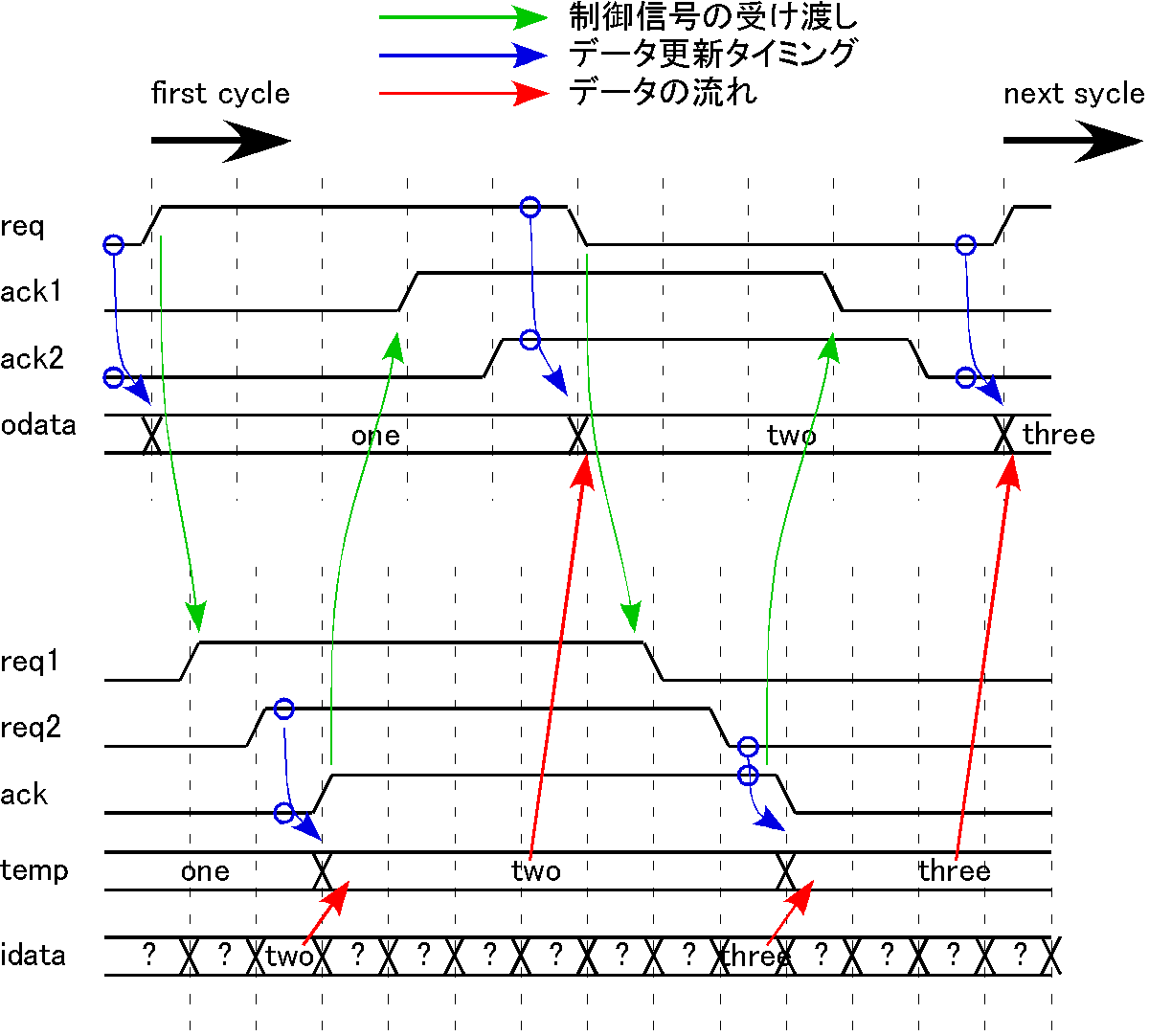

電気回路 Hdl 非同期信号を扱うための危ういverilogライブラリ 武内 筑波大

電子情報通信学会技術研究報告 Vol 119 No 373

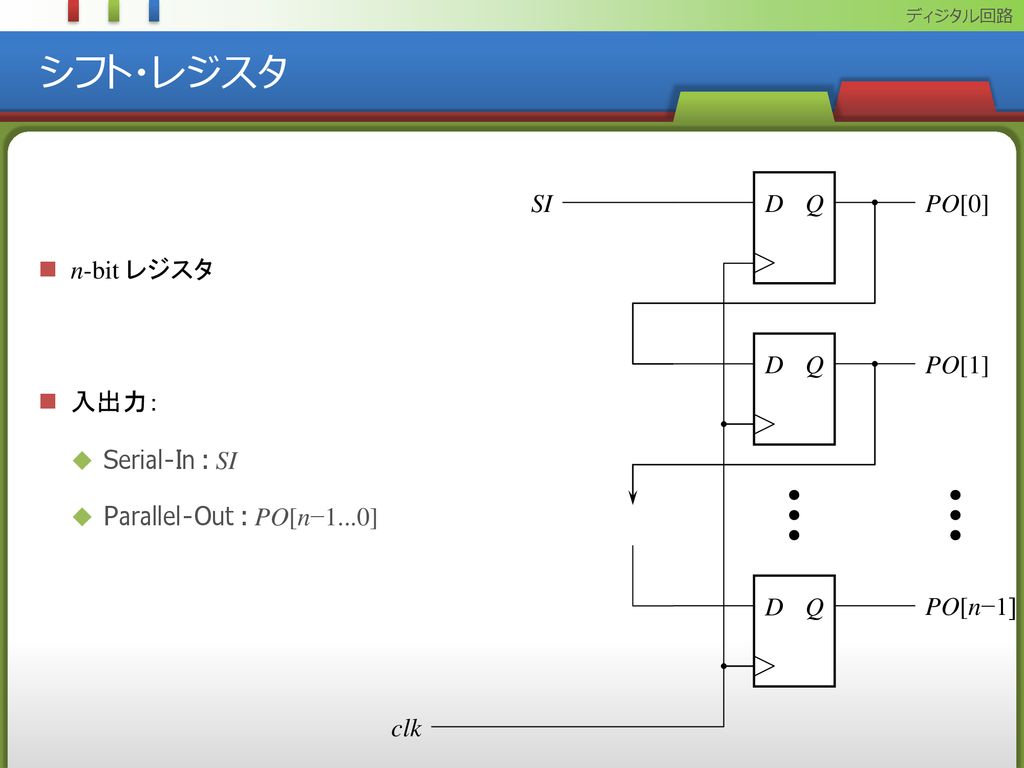

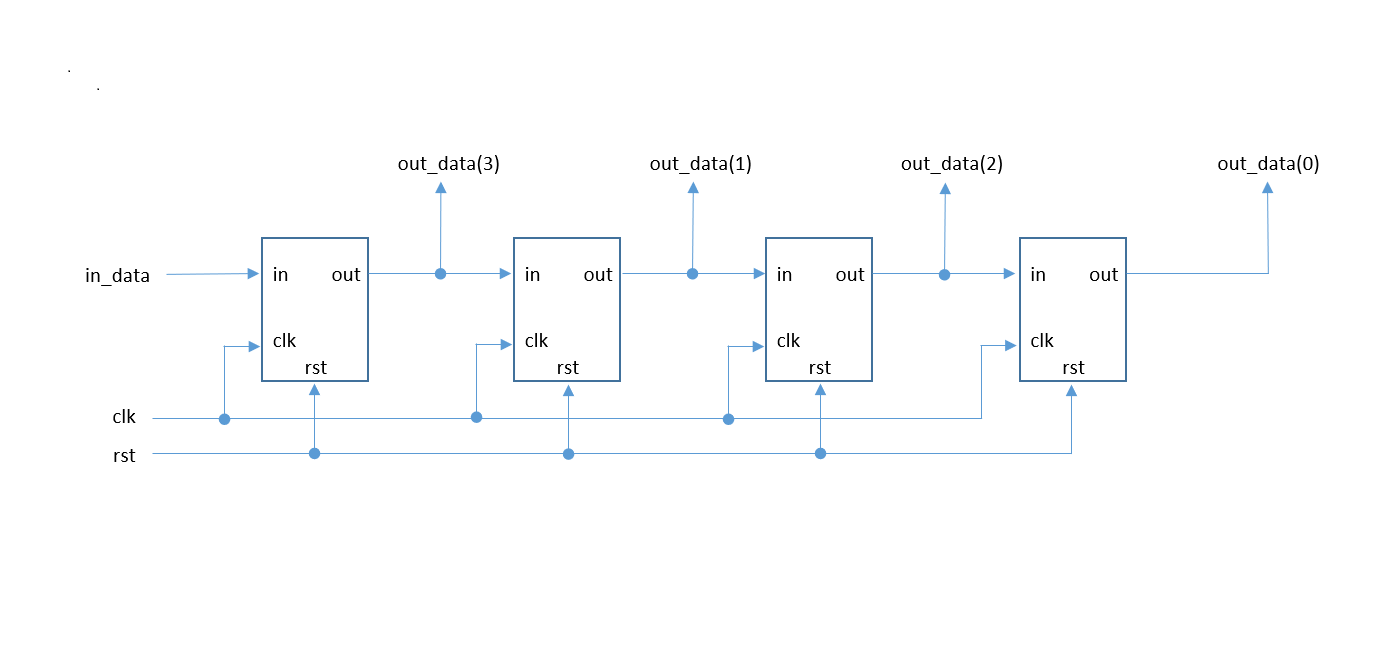

Feb 22, 21 · シフトレジスタの回路図と記述法 (verilog, VHDL) まずシフトレジスタとは、FF (フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。 よく使われる場面として、直列並列変換 (シリアルパラレル変換)があるかなと思います。 具体的にどういったものかは、言葉で書くよりタイミングチャートで示したほうがわかりやすいかと思うのシリアルデータ(クロック同期,8ビット固定長)をシフトレジスタで受信して、パラレルデータとして出力する。 全系はクロック(clk,100MHz)のみで動作させるため、遅いシリアルクロック(s_clk,10MHz)はサンプリングして立ち上がりエッジのパルス(s_clk_rise)を作り、このタイミングでシリアルイネーブルとデータをサンプリングする。 ブロック図 タイミングチャート Verilogシフトレジスタを用いてシリアルパラレル変換、パラレルシリアル変換を行えばよい。図5 はシフトレジスタを用いた、シリアルパラレル、パラレルシリアル変換回路の例である。 (1) シリアルパラレル変換回路 (2) パラレルシリアル変換回路 図5

メルカリ 入門verilog Hdl記述 ハードウェア記述言語の速習 実践 コンピュータ It 2 000 中古や未使用のフリマ

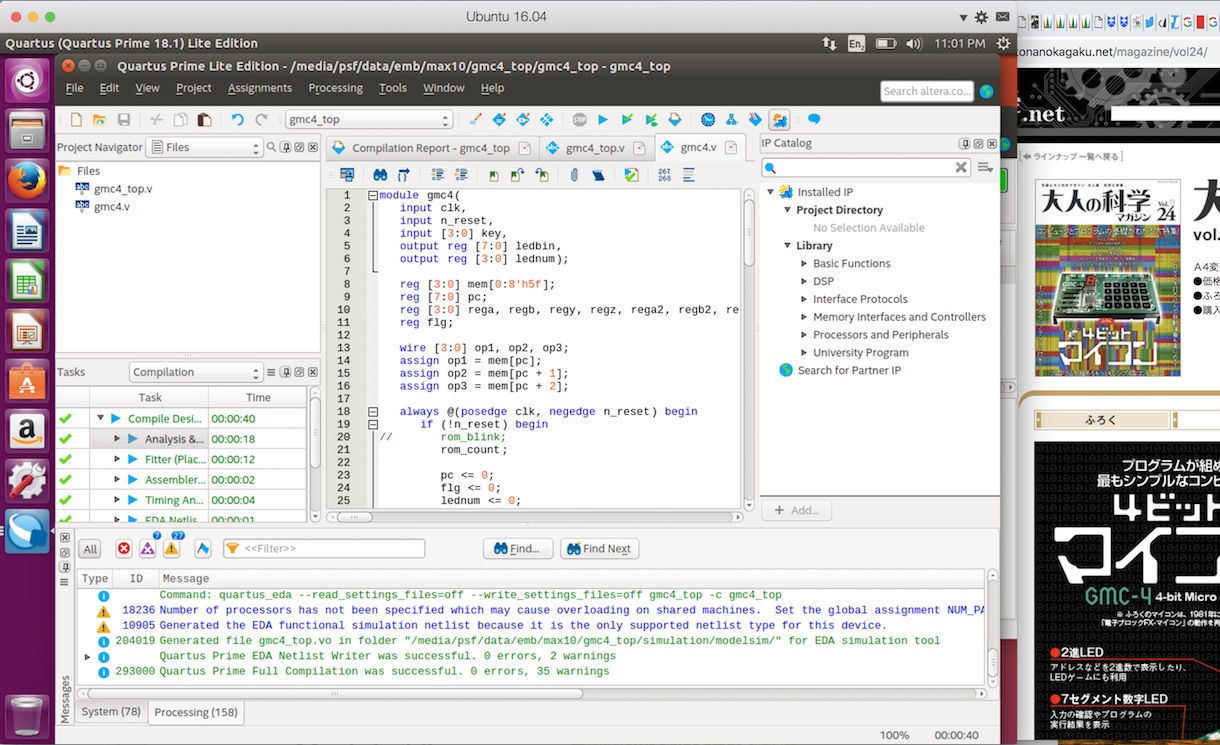

プログラムたった64行 Fpgaで創るオレオレ32bitcpu Tf32cpu R1 90mhz X 2コア動作 On Max10 Fpga Verilog Maker Kosen 福野泰介の一日一創 Create Every Day By Taisuke Fukuno

VerilogHDL で設計できるようになるために、以下のマテリアルを用意しています。 次に、シフト演算子です。 宣言部には、ポート宣言やレジスタ宣言、ネット宣言、パラメータ宣言を必要に応じApr 28, · シフトレジスタのサイズは、スタートビットとストップビットを含んだ10ビットとなります。 1ビット分、すなわち T ser の時間だけ待つことを担当するのが、図左側のカウンタです。指定したビット数に応じて左または右方向にビットをシフトさせます。 空いたビットには0が補完されます。 信号 >> シフト幅 // 符号なし右シフト

Todotaniのはやり物log 16年12月の記事

Idein Ideas Mobilenetv2のfpgaデモ

111 レジスタ 112 シフトレジスタ 演習 鹿間信介 摂南大学工学部電気電子工学科 論理回路Ⅱ 摂大・鹿間 レジスタとシフトレジスタ レジスタ データの一時記憶 シフトレジスタ 記憶したデータを 順次転送 リングカウンタ シフトレジスタを 円環状に接続 ff0Verilog シフトレジスタVerilog シフトレジスタのプログラム方法について質問があります。 (私は他の方向にシフトすることを知っています)。Aug 31, 13 · FPGAで4bitシフトレジスタ さて、FPGAでSFCコントローラの制御をするときに必要になるのはシフトレジスタだ。 まずは4bitシフトレジスタだ、ということでVerilog HDLで書いてみた。 自動制御に使ったTC74HC165APを参考にした。 大きな違いは、load端子がHighでロードすること。 ちょっと引っかかったのはブロッキング代入'='とノンブロッキング代入'

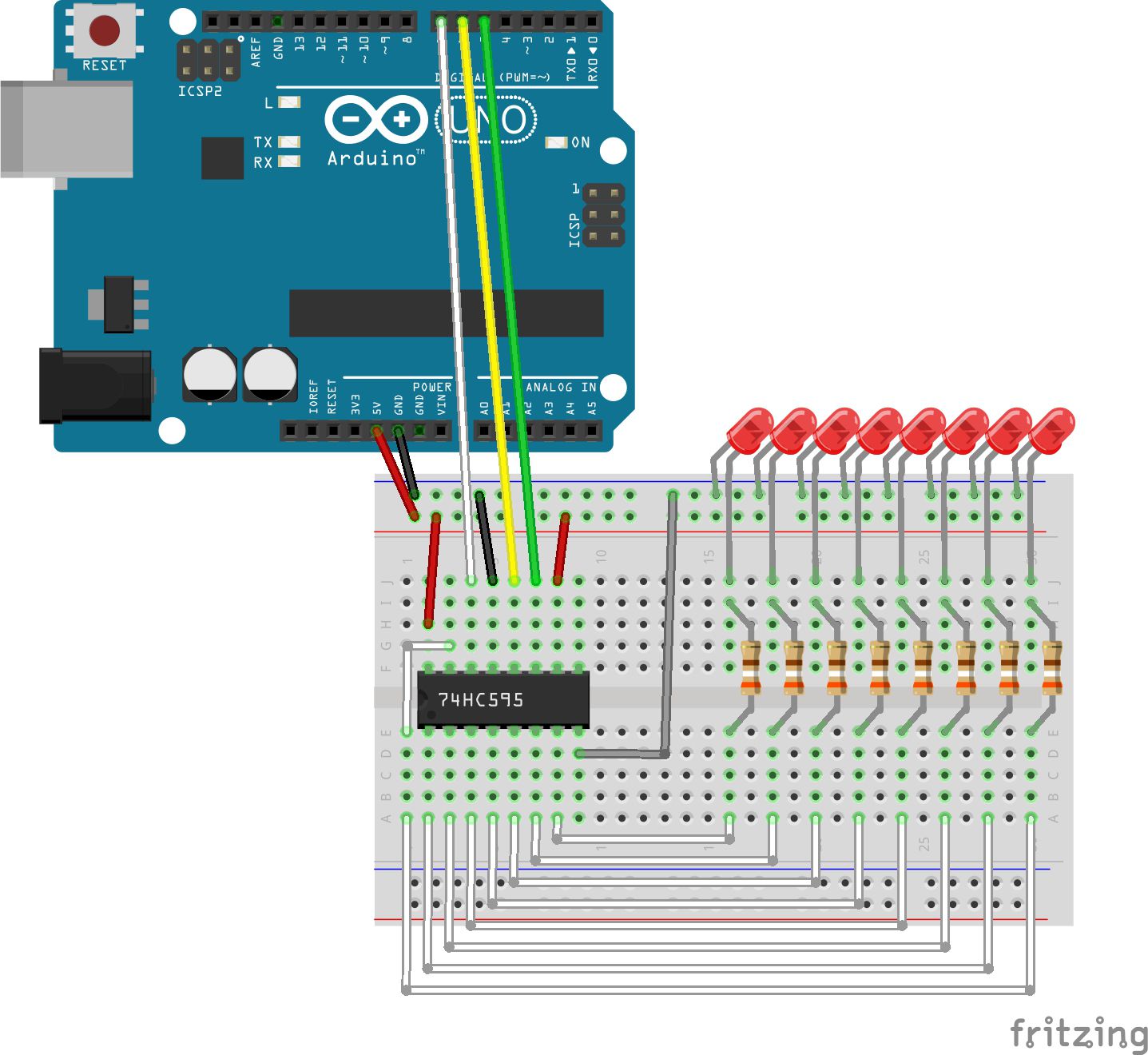

Arduinoでシフトレジスタ Sn74hc595 を使用して8個のledをチカチカさせる Stupiddog S Blog

デジタル回路設計veriloghdl通信講座 技術系通信講座のシーモス

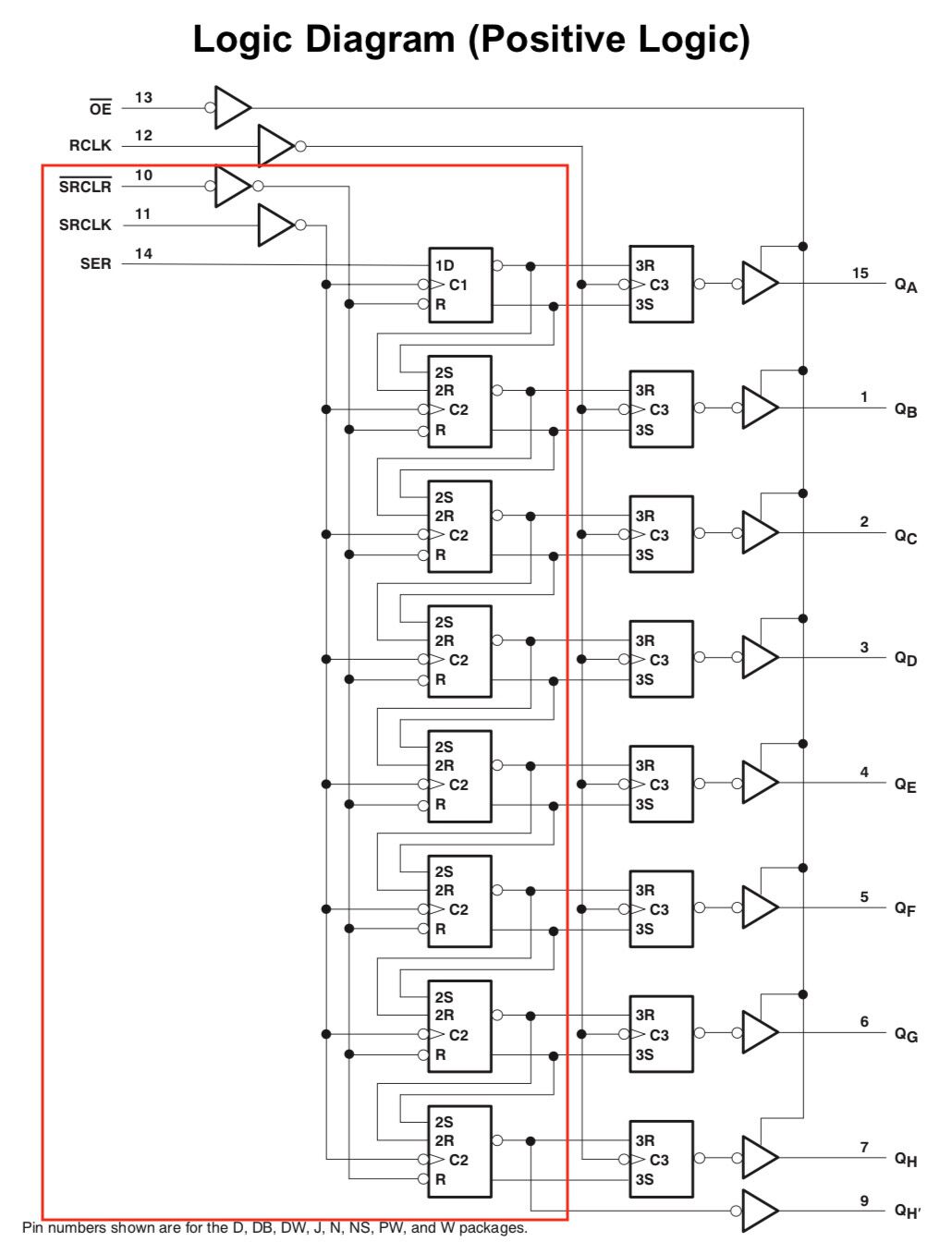

ShiftDR ステートを実行すると、TCKの立ち上がりエッジで、シフトレジスタ(Test Data Register)内のデータの1ビットシフトが実行され、TDiからデータが取り込まれ、シフトレジスタの最後のデータがTDoから出力されます。必要な回数分このステートを繰り返す代入文の意味 「代入文」 変数=式; 「式」:単独の定数や変数,配列要素,及び それらを演算記号で結合したもの。 記号「=」は,右辺の式の「値」を左辺の変数に「格納」するという作用をもつ。Sr4vhd : リスト8-1 「4ビットSIPOシフトレジスタ」 sr4evhd : リスト8-2 「4ビット同期イネーブル付きSIPOシフトレジスタ」 sr4levhd : リスト8-3 「4ビット(同期)パラレル・データ・ロード機能付きシフトレジスタ」

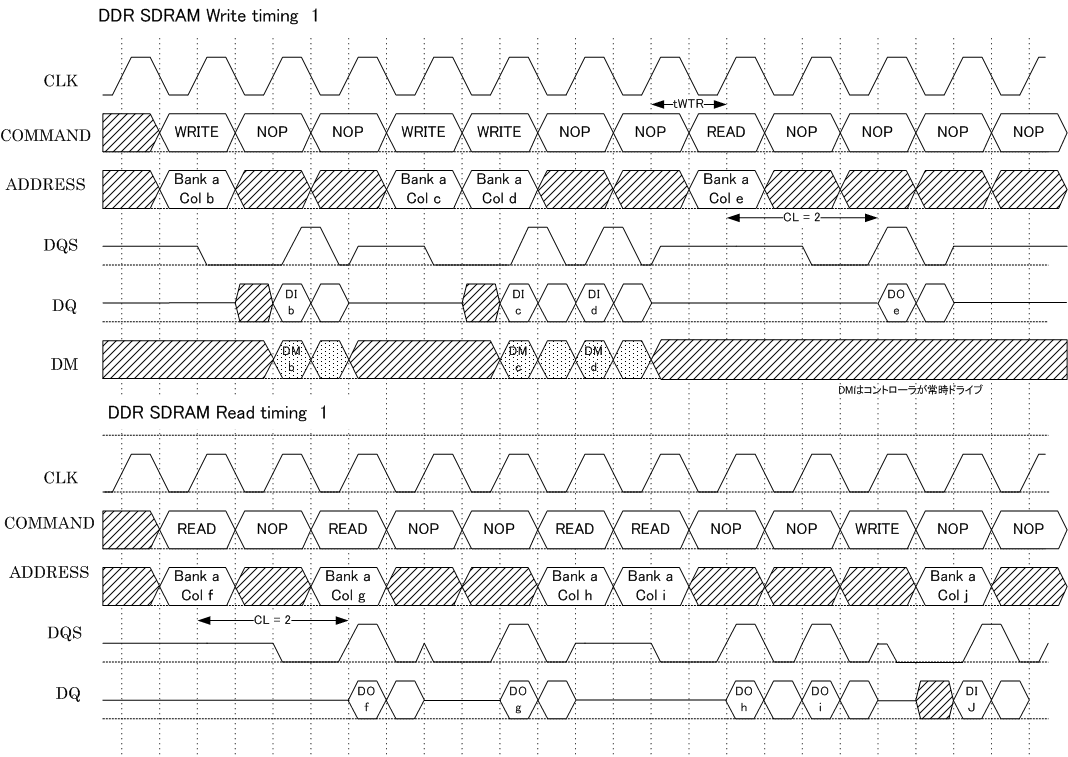

Spartan6版 Ddr2コントローラの作成 7

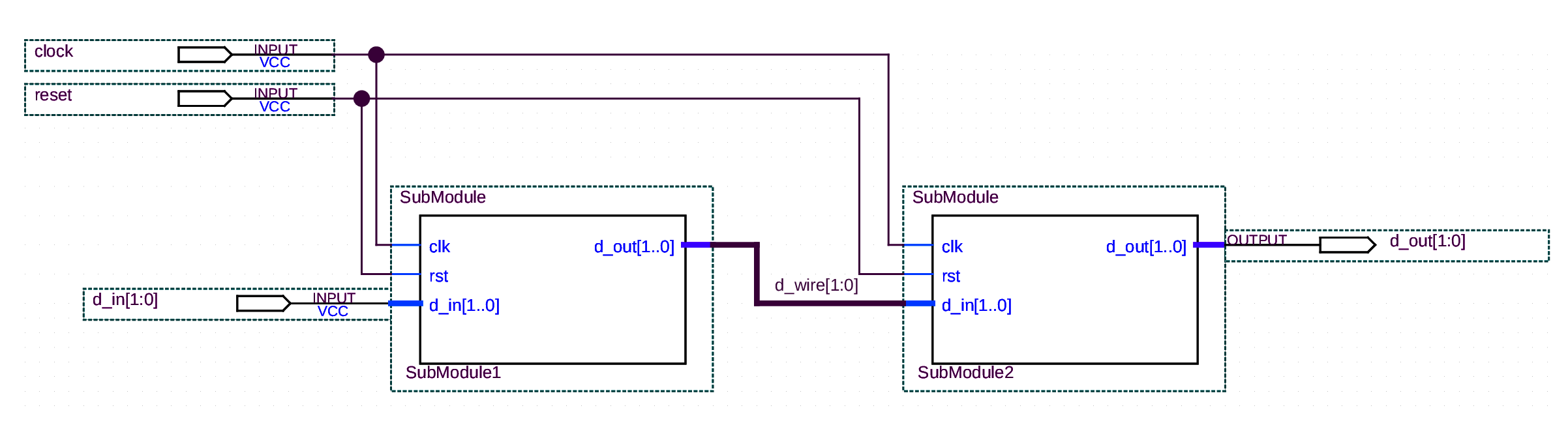

Vhdl Verilogによるコードベースからsimulinkによるモデルベースへ Pdf Free Download

Sep 04, 08 · 問題1 以下の回路をVerilog HDLで記述してください 答え. 解答はこちら (←クリック) 「完全マスター! 電子回路ドリル III」バックナンバーJul 10, 09 · リスト6(b)はイネーブル付きのシリアルパラレル変換シフト・レジスタです.連接演算を使ってシフト動作を実現しています. リスト6 カウンタとシフト・レジスタシフトレジスタで生成される符号 ― 巡画符号(ii)― 正会員 金 子 敏 信† 1 ま え が き 前回,巡 回符号を導入した今 回はそれに引き続 き,簡 単な巡回符号として単純パリティ検査符号,巡 回ハミング符号の紹介から始めるよ り複雑な巡回符

乗算器 その1 Hackmd

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

Feb 24, 21 · シフトレジスタの回路図と記述法 (verilog, VHDL) まずシフトレジスタとは、FF (フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。 よく使われる場面として、直列並列変換 (シリアルパラレル変換)があるかなと思います。 具体的にどういったものかは、言葉で書くより 論理回路 論理回路シフト レジスタは、合成およびシミュレーションにおいて VHDL または Verilog コードで初期化でき ます。 合成を行う場合、 16 ビット シフト レジスタ インスタンシエーションに INT 属性があるので、Jul 12, · 概要 遅延サイクルと幅を設定可能なシフトレジスタのVHDL版です。 FF生成は本モジュールをパラメーターを変えて使いまわすと楽そう。 ModelSimで動作確認、Vivado181にて実装確認をしました。 Shift Register Module ソースコード shift_regvhd shift_re

Fpgaの部屋 06年01月

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

16'h0000のときレジスタ型変数outはinをラッチします. countは16ビットなので,216クロック・サイクルに1回 だけ,このラッチが行われます.あとで,入力ポートclk に周期がns(周波数50MHz)のクロック信号を入力しま様に,次 のシフトでは001と なるさ らにシフト を続ければ,110,011,111,101と なるさ ら に,も う1回 シフトすれば,100の 初期状態に戻 る シフトレジスタの内容を時刻順に改めて書け ば,表1で あり,α0か らα6まで順次発生してい る 一般にm段 のシフトレジスタをJul 11, · シフトレジスタは普通このように1ビットデータを遅延させる構成になっています。

継続代入文

Fpga ジャジャガッチブログ

Jan , 19 · Python で書いた関数を Verilog HDL に変換する高位合成コンパイラである Polyphony を使ってみたいと思います。前回はクラス表記で port を指定しましたが、今回はもっと簡単に関数表記で port はお任せでフィボナッチ LFSRのアルゴリズムを Verilog に変換したいと思います。シミュレーション記述(test0v) 全加算器 1ビット全加算器による加算回路 4ビット バイナリ カウンタ 4ビット バイナリ カウンタ シミュレーション記述 1ビット カウンタ 1ビット カウンタ 4ビット シフトレジスタ8bit長のレジスタの、4ワード分の配列を宣言するには以下の通り。 reg 70 a03;

Fpga設計入門 Online Documentation For Altium Products

Systemverilog入門 篠塚 一也 著 文 共立出版 版元ドットコム

Verilog未経験者がatlysを動かしたときのメモ Fpga Qiita

Idein Ideas Mobilenetv2のfpgaデモ

シフトレジスタの回路図と記述法 Verilog Vhdl 組み込みエンジニアのメモ帳

Verilog 福野泰介の一日一創 Create Every Day By Taisuke Fukuno

15年04月 Fpgaの部屋

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

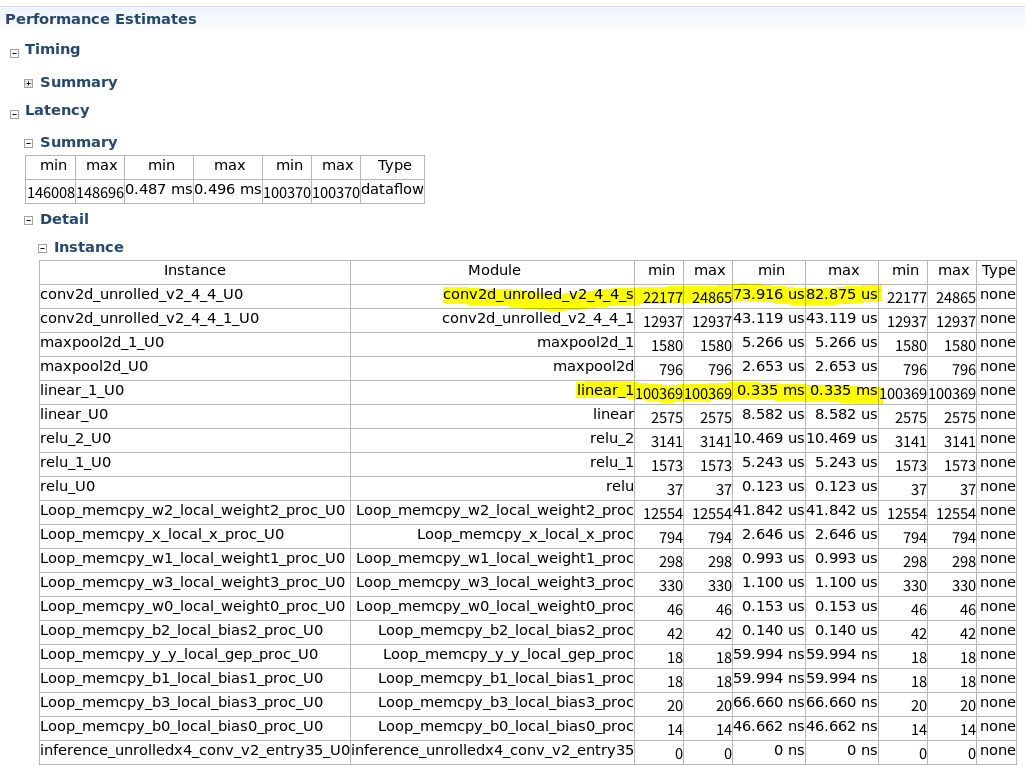

Fpga で始めるエッジディープラーニング 8 Acri Blog

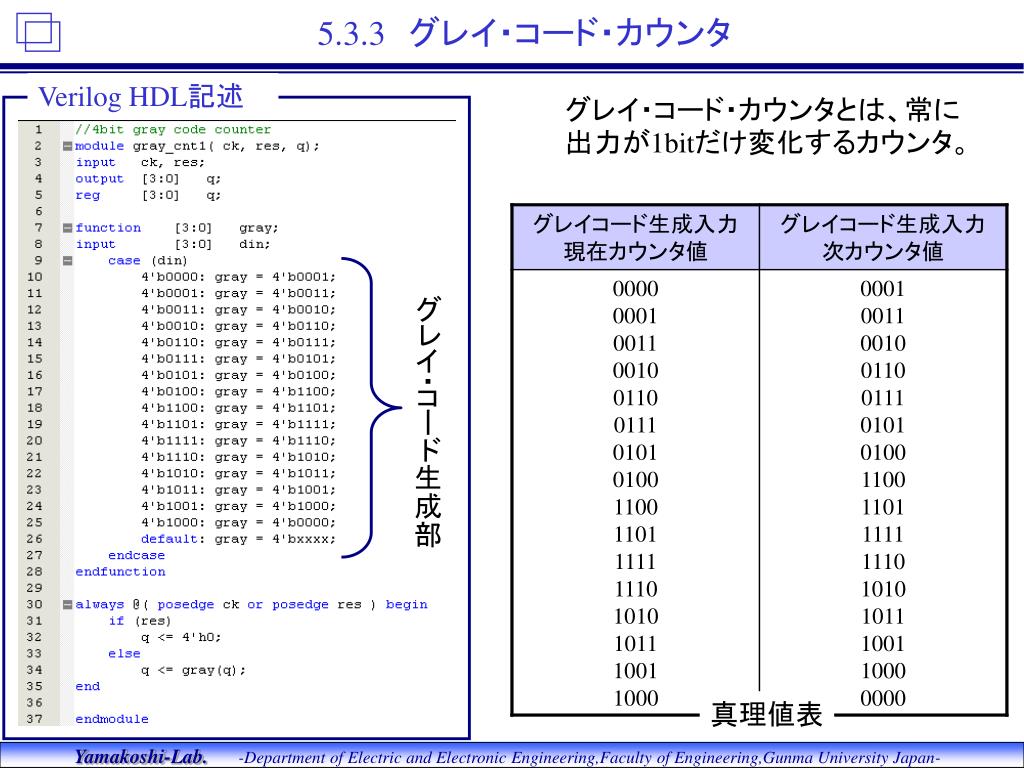

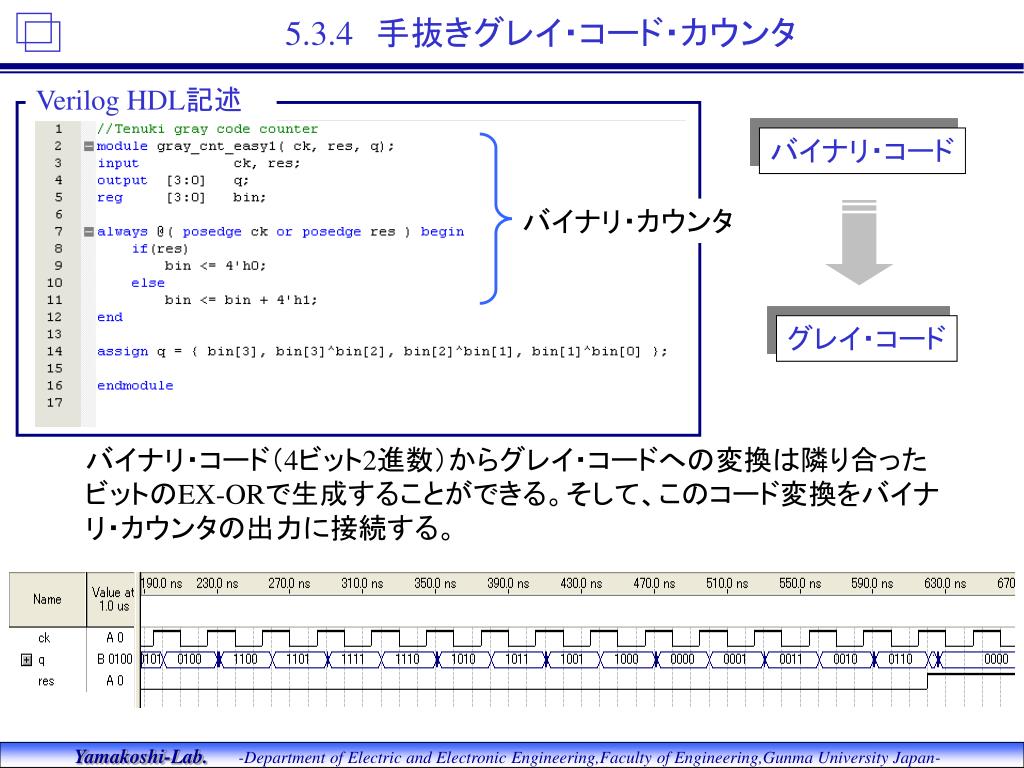

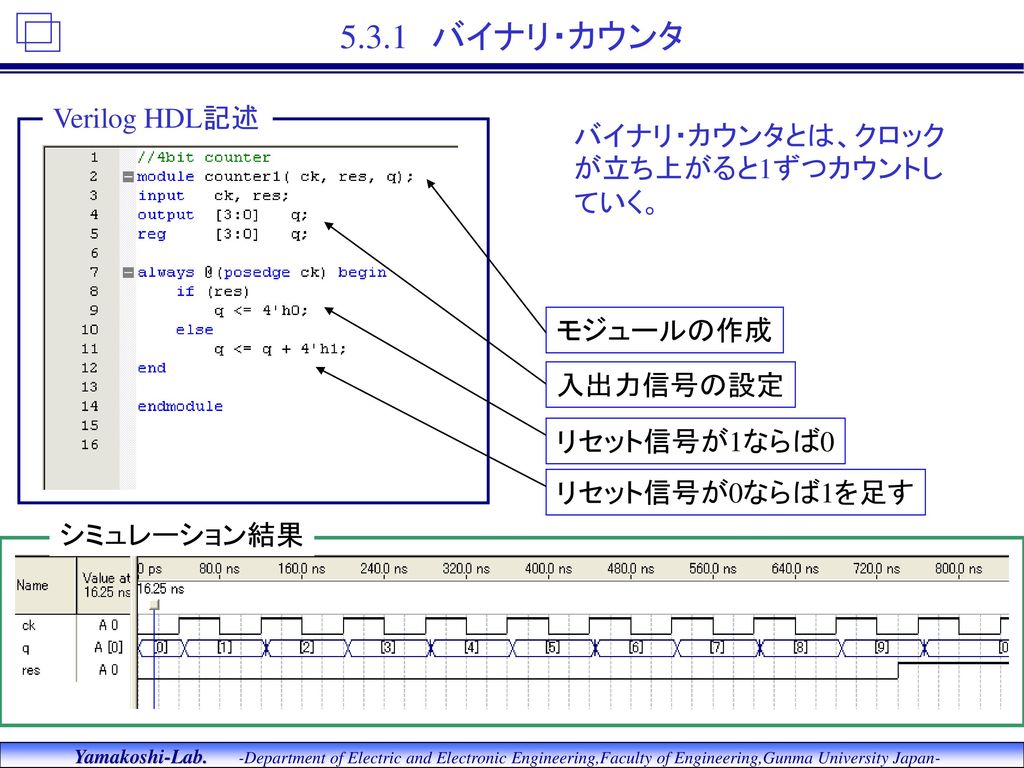

5 3 各種カウンタ 平木 Ppt Download

擬似乱数 M系列を使う1 Fpgaの部屋

Qflow Tutorial 株 アナジックス

Verilogとは コンピュータの人気 最新記事を集めました はてな

Verilog Hdlによる暗号ハードウェア

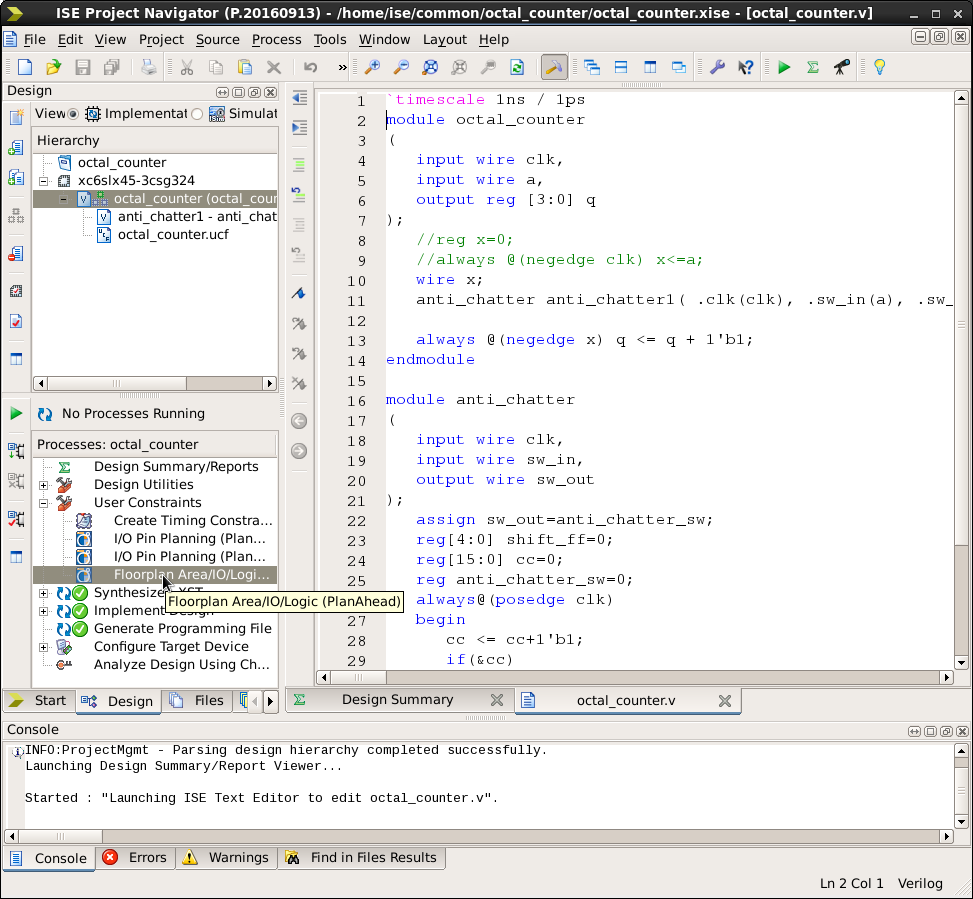

チャタリング除去

ディジタル論理回路 機能入門 電気 電子 本 雑誌 日刊工業新聞

情報工学実験第2 ハードウェア 実験 1 2

Fpga設計入門 Online Documentation For Altium Products

Verilog Hdl 入門編トライアル コース テキスト Pdf 無料ダウンロード

トコトンやさしいデジタル回路の本 電子回路 回路設計 デジタル回路 ビジネス 電気 電子 本 雑誌 日刊工業新聞

ディジタル回路 8 機能的な順序回路 五島 正裕 Ppt Download

Aki 中華fpgaボード Tang Primer を使ってfpgaとverilogに入門する本書きました 技術書典応援祭で出します 今朝完成しました もう少し後になりますが 応援祭開催中にサークルとしてテストベンチ本も出す予定です 技術書典 T Co

フリフリledのミニバージョン Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

Verilog未経験者がatlysを動かしたときのメモ Fpga Qiita

Fpga で始めるエッジディープラーニング 9 Acri Blog

An 307 Xilinx ユーザー向けのアルテラのデザイン フロー Manualzz

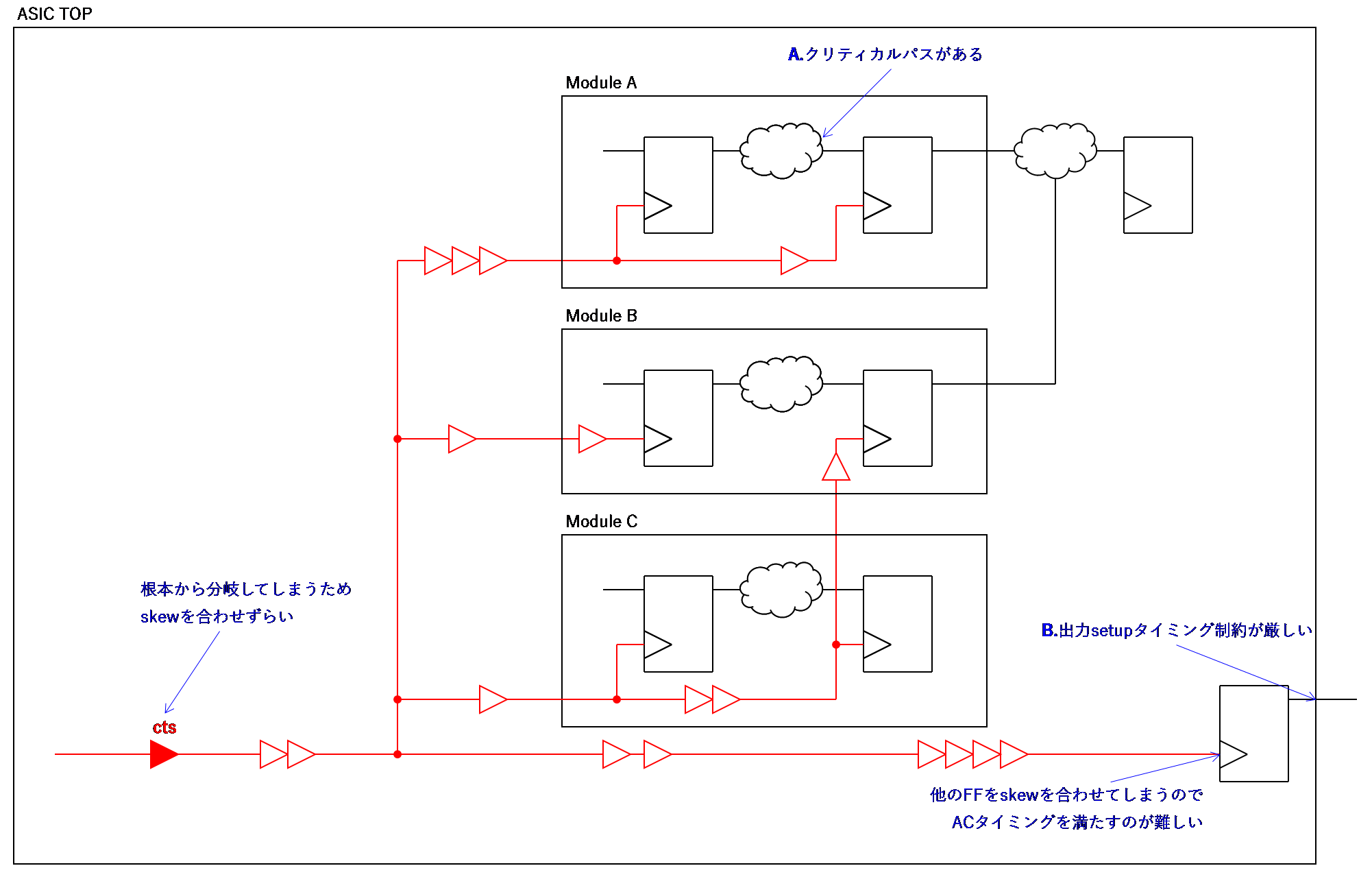

Asicの設計 開発コラム Kumico

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

An156 Psoc 3 Psoc 4 And Psoc 5lp Designing Psoc Creator Components With Udb Datapaths Japanese Pdf

Xcell Journal 日本語版 75 76 合併号 By Xcell Journal Japanese Issuu

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

Arduinoでシフトレジスタ Sn74hc595 を使用して8個のledをチカチカさせる Stupiddog S Blog

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

Hdlてにをは集

Ppt 5 3 各種カウンタ Powerpoint Presentation Free Download Id

Hdlてにをは集

情253 ディジタルシステム設計 6 Bert5 Ppt Download

シフトレジスタの回路図と記述法 Verilog Vhdl 組み込みエンジニアのメモ帳

新適当マイコン電子工作研究所 So Netブログ

Ppt 5 3 各種カウンタ Powerpoint Presentation Free Download Id

Verilog Hdl 入門編トライアル コース テキスト Pdf 無料ダウンロード

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

5 3 各種カウンタ 平木 Ppt Download

Qflow Tutorial 株 アナジックス

メルカリ 理論設計 Hdl 講義テキスト コミック アニメグッズ 1 568 中古や未使用のフリマ

Idein Ideas Mobilenetv2のfpgaデモ

デジタル回路設計veriloghdl通信講座 技術系通信講座のシーモス

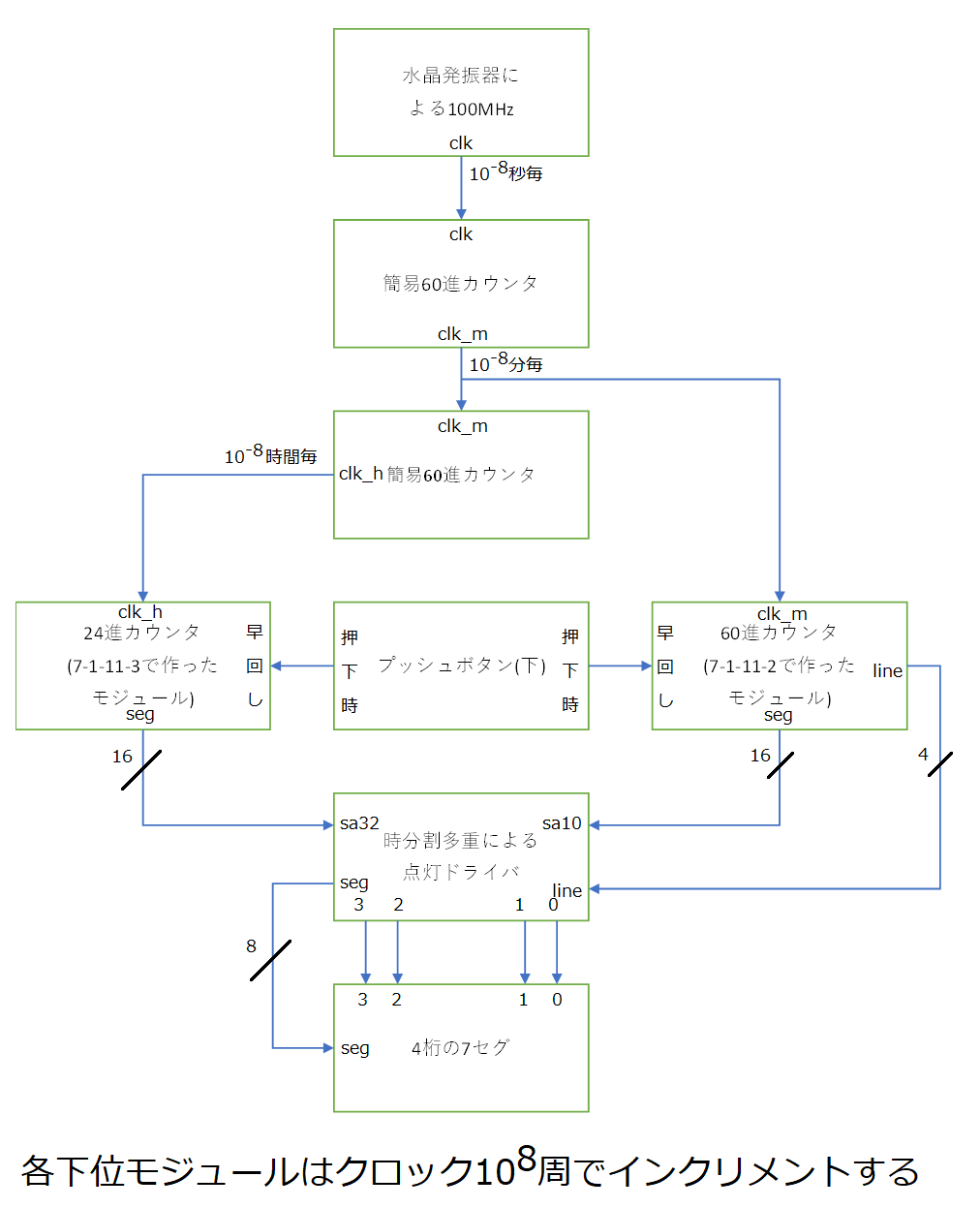

ドローン情報基盤システム 飛行情報共有機能 を覗いてみた Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

ほげめも Ddr Sdram コントローラを作った

0 件のコメント:

コメントを投稿